Analog electronics circuits miscellaneous

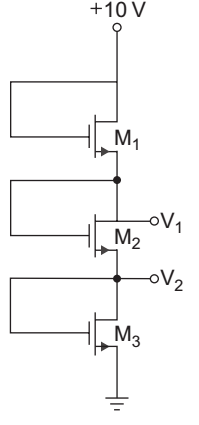

- In the circuit given below the transistor parameters are

VTN = 1 V, and kn = 36 µA/V2. If ID = 0.5 mA, V1 = 5 V and V2 = 2 V then the width-to-length ratio

i.e. W

required in each transistor is L

W

W

W

L 1 L 2 L 3

-

View Hint View Answer Discuss in Forum

For each transistor M1, M2 and M2

VGS = VDS i.e. VDS > VGS – VTN

Therefore all the transistor are in saturation Given that

VTN = 1 V

k′n = 36 µA/V2

ID = 0.5 mA

V1 = 5 VS V2 = 2 V

For transistor M3

V2 = 2V = VGS3

ID = 0.5 × 10–3= 1 36 × 10–6

W

. (2 – 1)2 2 L 3 after simplifying we get

W

= 27.8 L 3

For transistor M2,

VGS2 = V1 – V2 = 5 – 2 = 3 V

ID = 0.5 × 10–3= 36 × 10–6

W

(3 – 1)2 L 2 or

W

= 6.94 L 2

For transistor M1

VGS1 = 10 – V1 = 10 – 5 = 5 V

ID = 0.5 × 10–3= 1 36 × 10–6

W

. (5 – 1)2 2 L 1 or

W

= 1.74 L 1

Hence alternative (A) is the correct choice.Correct Option: A

For each transistor M1, M2 and M2

VGS = VDS i.e. VDS > VGS – VTN

Therefore all the transistor are in saturation Given that

VTN = 1 V

k′n = 36 µA/V2

ID = 0.5 mA

V1 = 5 VS V2 = 2 V

For transistor M3

V2 = 2V = VGS3

ID = 0.5 × 10–3= 1 36 × 10–6

W

. (2 – 1)2 2 L 3 after simplifying we get

W

= 27.8 L 3

For transistor M2,

VGS2 = V1 – V2 = 5 – 2 = 3 V

ID = 0.5 × 10–3= 36 × 10–6

W

(3 – 1)2 L 2 or

W

= 6.94 L 2

For transistor M1

VGS1 = 10 – V1 = 10 – 5 = 5 V

ID = 0.5 × 10–3= 1 36 × 10–6

W

. (5 – 1)2 2 L 1 or

W

= 1.74 L 1

Hence alternative (A) is the correct choice.

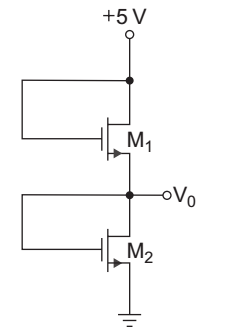

Direction: Consider the circuit shown below:

The both transistor have parameter as follows:

VTN = 0.8 V, kn = 30 ΩA/V2

-

If the ratio is

W

= 40 and

W

= 15, then V0 is: L 1 L 2

-

View Hint View Answer Discuss in Forum

According to question

W

= 40 and

W

= 15 L 1 L 2

Again

Kn1 (VGS1 – VTN1 )2=Kn2 (VGS2 – VTN2 )2

40 (VGS1 – 0.8)2 = 15 (VGS2 – 0.8)2 `…(A)

VGS1 + VGS2 = 5 …(B)

from (A) and (B)

40 (VGS1 – 0.8)2 = 15 (5 – VGS1 – 0.8)2

8 [V2GS1 +.64 –1.6 VGS1] = 3 [17.64 + V2GS1 –8 VGS1]

5 V2GS1 + 11.2 VGS1 – 47.8 = 0

VGS1 = 2.09

V0 = 5 – VGS1

= 5 – 2.09 = 2.91 V

Correct Option: A

According to question

W

= 40 and

W

= 15 L 1 L 2

Again

Kn1 (VGS1 – VTN1 )2=Kn2 (VGS2 – VTN2 )2

40 (VGS1 – 0.8)2 = 15 (VGS2 – 0.8)2 `…(A)

VGS1 + VGS2 = 5 …(B)

from (A) and (B)

40 (VGS1 – 0.8)2 = 15 (5 – VGS1 – 0.8)2

8 [V2GS1 +.64 –1.6 VGS1] = 3 [17.64 + V2GS1 –8 VGS1]

5 V2GS1 + 11.2 VGS1 – 47.8 = 0

VGS1 = 2.09

V0 = 5 – VGS1

= 5 – 2.09 = 2.91 V

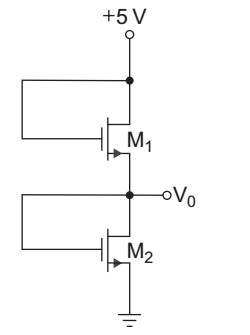

- If the width-to-length ratios of M1 and M2 are:

W

=

W

= 40 L 1 L 2

The output V0 is:

-

View Hint View Answer Discuss in Forum

For both transistor M1 and M2

VDS = VGS

∴ VDS > VGS – VTN therefore both the transistor are in saturation

ID1 = ID2

ID1 = Kn1 (VGS1 – VTN1 )2

= Kn2 (VGS2 – VTN2)2 …(A)

Kn1 = Kn2 and VTN1 = VTN2

on expanding equation

V2GS1 + V2TN1 – 2VGS1 = V2GS2 + V2TN2 – 2VGS2

or V2GS1 + V2GS2 = 2 (VGS1 – VGS2) …(B)

from given figure,

VGS1 + VGS2 = 5 …(C)

V2GS1 – (5 – VGS1 )2 = 2 (VGS1 – VGS1 + 5)

V2GS1 – 25 – V2GS1 + 10 VGS1 = 10

10 VGS1 = 35

or VGS1 = 3.5

VGS2 = 5 – VGS1 = 5 – 3.5 = 1.5 V

So, V0 = 5 – VGS1 = VGS2 = 1.5 V

Correct Option: A

For both transistor M1 and M2

VDS = VGS

∴ VDS > VGS – VTN therefore both the transistor are in saturation

ID1 = ID2

ID1 = Kn1 (VGS1 – VTN1 )2

= Kn2 (VGS2 – VTN2)2 …(A)

Kn1 = Kn2 and VTN1 = VTN2

on expanding equation

V2GS1 + V2TN1 – 2VGS1 = V2GS2 + V2TN2 – 2VGS2

or V2GS1 + V2GS2 = 2 (VGS1 – VGS2) …(B)

from given figure,

VGS1 + VGS2 = 5 …(C)

V2GS1 – (5 – VGS1 )2 = 2 (VGS1 – VGS1 + 5)

V2GS1 – 25 – V2GS1 + 10 VGS1 = 10

10 VGS1 = 35

or VGS1 = 3.5

VGS2 = 5 – VGS1 = 5 – 3.5 = 1.5 V

So, V0 = 5 – VGS1 = VGS2 = 1.5 V

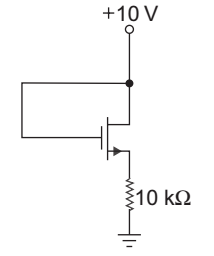

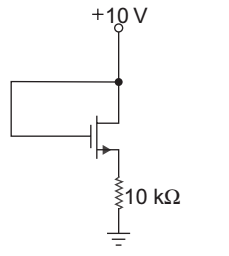

- The parameters for the transistor in circuit of fig. below are VTN = 2 V and Kn = 0.2 mA/V2. The power dissipated in the transistor is:

-

View Hint View Answer Discuss in Forum

From fig. since gate is connected to the drain. Hence transistor will always in saturation.

ID = 10 – VGS = Kn (VGS – VTn)2 10 kΩ

10 – VGS = 0.2 × 10–3 × 10 × 103 (VGS – 2)2

or 10 – VGS = 2 (VGS – 2)2

After solving quadratic equation, we get

VGS = – 0.27 V, 3.77 V VGS = – 0.27 is not possible since gate terminal is at 10 V. So, VGS = 3.77 V is taken

i.e. VGS = VDS = 3.77 VID = 10 – 3·77 = 0.623 mA 10 kΩ

Power = ID VDS = 0.623 × 10–3 × 3.77 = 2.35 mW

Correct Option: B

From fig. since gate is connected to the drain. Hence transistor will always in saturation.

ID = 10 – VGS = Kn (VGS – VTn)2 10 kΩ

10 – VGS = 0.2 × 10–3 × 10 × 103 (VGS – 2)2

or 10 – VGS = 2 (VGS – 2)2

After solving quadratic equation, we get

VGS = – 0.27 V, 3.77 V VGS = – 0.27 is not possible since gate terminal is at 10 V. So, VGS = 3.77 V is taken

i.e. VGS = VDS = 3.77 VID = 10 – 3·77 = 0.623 mA 10 kΩ

Power = ID VDS = 0.623 × 10–3 × 3.77 = 2.35 mW

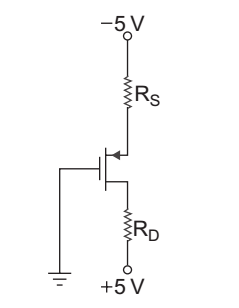

- The PMOS transistor shown below has parameters:

VTP = - 1.2 V, W = 20, and KP = 30 µA/V2 L

If ID = 0.5 mA and VD = – 3 V, then value of RS and RD are:

-

View Hint View Answer Discuss in Forum

NA

Correct Option: D

NA